## МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ УКРАИНЫ СУМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

### А.А. БОРИСЕНКО

# БИНОМИАЛЬНЫЕ АВТОМАТЫ

СУМЫ ИЗД-ВО СУМГУ 2005

#### **ВВЕДЕНИЕ**

Данное учебное пособие предназначено в первую очередь студентам специальности "Электронные системы", но может быть применено и для других специальностей, таких, например, как "Электронные вычислительные машины" для чтения в курсах "Цифровая схемотехника" и "Цифровые автоматы", а также для курсового и дипломного проектирования бакалаврами, специалистами и магистрами. Кроме того, оно будет полезно инженерам и научным работникам, которые занимаются проектированием электронной аппаратуры.

Изложенные в пособии структуры цифровых автоматов представляют собой отредактированные статьи и изобретения автора для биномиального цифрового счета и преобразования информации. За прошедшее время эти работы не только не устарели, а даже приобрели дополнительную актуальность, так как в связи с появлением достаточно сложных программируемых логических интегральных схем (ПЛИС) появилась возможность их эффективной реализации во многих цифровых устройствах и системах - от устройств для мобильной связи и до электронных систем управления.

Но все же главное назначение данной работы — это попытка привить студентам интерес к творческой работе на примерах нестандартных решений электронных цифровых устройств, которые являются практическим результатом специальной математической теории.

Пособие состоит из четырех глав. Первая из них представляет собрание отредактированных статей автора по двоичным биномиальным системам счисления, а также алгоритмам и устройствам на их основе. Начинается она первой работой по биномиальным системам счисления, депонированной во ВИНИТИ, а заканчивается примером реализации биномиального счетчика с помощью микропроцессорного устройства.

Вторая глава представляет собой переработанные автором описания изобретений двоичных биномиальных счетчиков. Следует отметить, что производство счетчиков и цифровых устройств на их основе представляет на сегодня целую индустрию, в которую входят специализированные фирмы и организации, выпускающие механические, электромеханические и электронные счетчики, а также программновременные задатчики и электронные часы. Наряду с этим счетчики как составные элементы входят в большинство электронных цифровых

устройств и представляют собой наиболее массовый вид микроэлектронных устройств. Им посвящены отдельные книги и научные работы.

В третьей главе рассматриваются счетчики равновесных кодов, отличающиеся повышенной надежностью и быстродействием. В их основе лежат биномиальные структуры.

Четвертая глава содержит информацию о специальных биномиальных преобразователях, позволяющих получать равновесные коды и производить их нумерацию. На этой основе решены задачи сжатия двоичной информации и предложены соответствующие ей цифровые устройства с возможностью защиты сообщений от несанкционированного доступа. Такие устройства, будучи размещенными в одной микросхеме и отличаясь высоким быстродействием и надежностью, способны производить сжатие и защиту информации в реальном масштабе времени.

Данные разработки, признанные изобретениями, используют оригинальные решения биномиальных счетчиков, рассмотренные в предыдущей главе. Они могут быть применены для рейтинговых курсовых проектов повышенной сложности и стать темой дипломных проектов и магистерских работ, а при дальнейшем совершенствовании, и диссертаций. Собственно, все эти разработки, так или иначе, уже использовались ранее в диссертациях.

В заключение следует отметить, что за последние 50 лет в повседневно используемой цифровой электронной технике не произошло принципиальных изменений ее основ. Шел прогресс в области повышения ее быстродействия и качества, расширялись области применения, вводились новые сервисные функции, однако основные идеи, высказанные еще фон Нейманом, оставались неизменными. Одной из главных среди них оставалась идея использования в электронных устройствах двоичной системы счисления.

В данной работе в отличие от традиционных структур представлены устройства, использующие в своей основе не двоичную, а биномиальную систему счисления, хотя и с двоичным алфавитом. Ее недостаток — относительно высокая сложность - одновременно является и ее достоинством. При современном уровне интегральной технологии можно получать качественно новые по своей структуре и возможностям цифровые устройства практически любой сложности без существенного повышения уровня их цен.

Такими возможностями этих структур являются их повышенная надежность, улучшенная диагностируемость и высокое быстродействие. Кроме того, они позволяют выполнять новые функции, трудно достигаемые обычными средствами, например, с их помощью можно достичь одновременно высокого коэффициента сжатия информации и высокой стойкости ее защиты.

Заканчивая данное введение, следует отметить, что биномиальные устройства не ограничиваются только схемами, приведенными в данной работе, так как, кроме них, спроектированы еще и биномиальные устройства, основанные на разработанной автором многозначной биномиальной системе счисления. Однако это уже другая тема, выходящая за рамки данной книги.

## ГЛАВА 1 ДВОИЧНЫЙ БИНОМИАЛЬНЫЙ СЧЕТ

# 1.1 Система счисления с "биномиальным" основанием и двоичным алфавитом

Депонированная рукопись №909-82. Деп Борисенко А. А.

В последние годы появились работы, в которых основанием системы счисления выступают функциональные зависимости, например, "фибоначчиева" [1]. Эти системы имеют ряд особенностей и досточиств, не присущих "естественным" системам счисления.

Данная работа дополняет системы счисления с функциональным основанием. В рассматриваемом случае в качестве основания системы счисления используется выражение для биномиальных коэффициентов (сочетание k элементов из  $n-C_n^k$ ), а сама система счисления определяется как "биномиальная".

Кодообразующая функция имеет вид

$$F = a_j C_{n-1}^k + a_{j-1} C_{n-2}^{k-a_j} + \dots + a_0 C_{n-j}^{k-q},$$

(1)

где

$$q = \sum_{\gamma=1}^{j} a_{\gamma},$$

$$a_{\gamma} = \begin{cases} 1, \\ 0. \end{cases}$$

(2)

На основании равенств (1) и (2) получим, что максимальное "биномиальное" число

$$F_{\langle \delta u \mu \rangle}^{\max} = 111...1 = C_{n-1}^k + C_{n-2}^{k-1} + ... + C_{n-k+1}^{k-k+1} = C_n^k - 1.$$

(3)

Следовательно, диапазон представимых в "биномиальной" системе счисления чисел, учитывающий и нуль, равен  $C_n^k$ .

Представленные в "биномиальной" системе счисления числа должны удовлетворять одной из систем ограничений:

$$\begin{cases} k = \sum_{\gamma=1}^{j} a_{\gamma}, \\ j < n \end{cases}$$

(4)

или

$$\begin{cases} k < \sum_{\gamma=1}^{j} a_{\gamma}, \\ j = n - k + \sum_{\gamma=1}^{j} \alpha_{\gamma}. \end{cases}$$

(6)

$$j = n - k + \sum_{\gamma = 1} \alpha_{\gamma}. \tag{7}$$

Ограничения (4) и (5) показывают, что число единиц необходимых, для однозначного представления числа "биномиальным" кодом, подчиняющимся этим ограничениям, равно k.

Из ограничения (5) следует, что наибольшее значение *ј* равно n-1. Следовательно, максимальное число нулей в "биномиальных" кодовых комбинациях будет равно n-k-1. Кроме того, "биномиальные" кодовые комбинации, зависящие от ограничений (4) и (5), должны заканчиваться единицами. В противном случае не будет выполняться ограничение (4).

Ограничение (7) показывает, что число нулей, необходимых для однозначного представления числа в "биномиальном" коде, должно равняться n - k. В этом случае

$$j = n - k . (8)$$

Из ограничения (6) следует, что наибольшее число единиц в комбинациях "биномиального" кода равно k-1. Сумма максимального числа нулей и единиц в "биномиальном" коде определит наибольшую длину кодовой комбинации, удовлетворяющую системе ограничений (6), (7):

"Биномиальные" кодовые комбинации, удовлетворяющие ограничениям (6) и (7), должны заканчиваться нулем. Число единиц для различных кодовых комбинаций не одинаково. Оно изменяется от 0 до k-1. Число же нулей является постоянным и равным n-k. Это следует из ограничения (7).

Таким образом, двоичные "биномиальные" кодовые комбинации разбиваются на два класса:

- а) кодовые комбинации, оканчивающиеся единицами, содержащие k единиц и переменное число нулей, изменяющееся в пределах от 0 до n-k-1;

- б) кодовые комбинации, оканчивающиеся нулем, содержащие n-k нулей и переменное число единиц, изменяющееся в пределах от 0 до k-1.

**Пример 1** Допустим n = 6, k = 4. В кодовой комбинации, удовлетворяющей ограничениям (6) и (7), содержатся две единицы. Определить длину кодовой комбинации, привести их возможные варианты и найти эквивалентное представление в десятичном коде.

**Решение.** В соответствии с выражением (7) длина "биномиального" кода j = 6 - 4 + 2 = 4.

Следовательно, в коде числа должно содержаться два (n-k=2) нуля и две единицы, причем код должен заканчиваться нулем. Соответствующие варианты кодов чисел в порядке их возрастания приведены ниже:

0110, 1010, 1100.

На основании равенства (1) представим полученные коды в десятичной форме:

$$0110 = 0 \cdot C_5^4 + 1 \cdot C_4^4 + 1 \cdot C_3^3 + 0 \cdot C_2^2 = 2,$$

$$1010 = 1 \cdot C_5^4 + 0 \cdot C_4^3 + 1 \cdot C_3^3 + 0 \cdot C_2^2 = 6,$$

$$1100 = 1 \cdot C_5^4 + 1 \cdot C_4^3 + 0 \cdot C_3^2 + 0 \cdot C_2^2 = 9.$$

"Биномиальный" код позволяет сравнительно легко переходить от кодовых комбинаций к соответствующим им сочетаниям. Для этого достаточно приписать к коду недостающие единицы или нули.

**Пример 2** Даны "биномиальные" коды чисел:  $A^1_{\langle \delta \rangle} = 01111$ ,  $A^0_{\langle \delta \rangle} = 00$ ,  $A^6_{\langle \delta \rangle} = 1010$ . Требуется определить соответствующие им сочетания.

**Ответ.**

$$A^1_{\langle \delta \rangle} = 011111\underline{0}$$

,  $A^0_{\langle \delta \rangle} = 00\underline{1111}$ ,  $A^6_{\langle \delta \rangle} = 1010\underline{11}$ .

Приписанные нули и единицы подчеркнуты.

Обратная задача перехода от сочетаний к "биномиальным" кодам решается отбрасыванием лишних в соответствии с ограничениями (4, 5, 6, 7) нулей и единиц, т.е. до получения n-k нулей или k единиц.

"Биномиальное" число затем в соответствии с выражением (1) можно перевести в естественную систему счисления. Тем самым решается задача нумерации сочетаний.

Пример 3 Найти номер сочетания 10011.

**Решение.** В произведенном сочетании трех единиц из пяти элементов вычеркиваем единицы до получения первого из двух нулей. Тем самым получаем "биномиальное" число  $A_{\langle \delta \rangle} = 100$ .

Затем в соответствии с выражением (1) преобразовываем его в десятичную систему счисления:

$$A_{\langle \delta \rangle} = 100 = A_{\langle 10 \rangle} = 1 \cdot C_5^4 + 0 \cdot C_4^3 + 0 \cdot C_3^3 = 5$$

.

Ответ. Номер сочетания 10011 равен 5.

### Список литературы

1. Стахов А.П. Введение в алгоритмическую теорию измерения.-М.: Советское радио, 1977.

# 1.2 О некоторых возможностях позиционных систем счисления

А. А. Борисенко, канд. техн. наук, С. И. Губарев, канд. техн. наук Автоматизированные системы управления и приборы автоматики, Харьков,  $N \ge 82$ , 1987 г.

В вычислительной технике широко распространены степенные позиционные системы счисления. Более сложные системы, в которых зависимость между весом разряда и его номером отличается от степенной (обобщенные позиционные системы счисления), менее известны и не нашли еще достаточного применения. Исследование этих систем выявило ряд полезных свойств, например: помехоустойчивость, возможность генерирования перестановок [1, 2].

Практическое применение обобщенных позиционных систем счисления (ОПСС) основывается на двух их важнейших свойствах: ОПСС позволяют формировать и нумеровать комбинаторные объекты различной природы; ОПСС являются помехоустойчивыми.

В результате на их основе можно разрабатывать специализированные управляющие устройства с экстремальными характеристиками по быстродействию, надежности, габаритам, весу; строить адаптивные коды и кодирующие устройства для сквозного контроля информации относительно ошибок в процессе ее преобразования, передачи и хранения; разрабатывать алгоритмы и устройства для сжатия и засекречивания информации; предложить новые, более эффективные по быстродействию алгоритмы и реализующие их устройства для решения ряда задач комбинаторной оптимизации.

Разработка специализированных управляющих устройств основывается на разработке такой ОПСС, структура которой в максимальной степени соответствует специфике решаемой задачи. Таким образом происходит экономия аппаратурных затрат и достигается значительный выигрыш в быстродействии (в десятки и сотни раз по сравнению с универсальными ЭЦВМ). Так как ОПСС являются помехоустойчивыми, то наряду с повышением быстродействия и снижением стоимости устройств повышается их надежность и упрощается диагностика неисправностей.

Целесообразно на основе ОПСС разрабатывать управляющие

устройства, которые выполняют в основном логические и простейшие арифметические операции над целыми числами. Это вызвано тем, что указанные операции в ОПСС выполняются наиболее эффективно. Отдельные узлы таких специализированных устройств представляют самостоятельный интерес для универсальных ЦВМ, например, помехоустойчивые счетчики, регистры, АЦП [2]. Однако их конкурентоспособность с аналогичными двоичными узлами возможна, как правило, при интегральном исполнении. Поэтому для каждого конкретного случая применения узлов, работающих в ОПСС в универсальной ЦВМ, требуется тщательная оценка их комплексной эффективности по всем параметрам.

Для решения задачи помехоустойчивого хранения и передачи информации разработано довольно большое количество различных кодов, как обнаруживающих, так и исправляющих ошибки. На практике в своем подавляющем большинстве нашли применение коды для обнаружения ошибок при передаче и хранении информации. Среди указанных кодов особо следует выделить коды, обнаруживающие ошибки не только при передаче и хранении, а и во время обработки информации. Это арифметические коды и коды в системе остаточных классов. К такому классу кодов относятся и коды чисел в ОПСС. Их достоинства - простота алгоритмов и устройств обнаружения ошибок, регулярность структуры, высокая помехоустойчивость, возможность регулирования избыточности кода и соответственно обнаруживающей способности в зависимости от состояния канала связи (адаптивность), помехоустойчивость кодирующих и декодирующих устройств. Применение этих кодов приобретает особое значение в специализированных автоматических системах управления. Съем информации, ее обработка, передача и выработка управляющих воздействий происходят в одном и том же коде ОПСС. В результате можно наряду с повышением помехоустойчивости получить выигрыш в аппаратуре, быстродействии и габаритах. Этим не ограничиваются возможности кодов в ОПСС. Важное их свойство - способность формирования комбинаторных кодов, например: равновесных, сменно-посылочных, сменно-качественных и т. д. [3].

Одной из актуальных задач при хранении и передаче информации является ее сжатие. В настоящее время существует довольно широкий арсенал средств ее решения, что не исключает разработки новых или усовершенствования старых. Одно из них - нумерация

сообщений. Основные достоинства нумерации - алгоритмический характер кодирования, позволяющий легко осуществить его техническую реализацию, а также отсутствие потребности в словаре. ОПСС позволяют расширить класс нумеруемых сообщений и упростить алгоритмическую и аппаратную реализацию задачи сжатия сообщений. Однако применение нумерационного кодирования наталкивается на трудности, связанные с ростом разрядности кодируемых сообщений. Существует другой путь сжатия информации, не требующий применения словаря, - оптимальное кодирование на основе кодов Шеннона - Фано и Хаффмана [3, 4]. При их использовании возникает необходимость в предварительных статистических испытаниях для выявления распределения частот символов передаваемых сообщений. Эти частоты при ограничениях на длину сообщений отражают истинное распределение вероятностей символов со значительной погрешностью. Поэтому оптимальное кодирование не отличается большой эффективностью сжатия. Ее повышение возможно путем замены определения частот символов вычислением их вероятностей на основе ОПСС. В таком случае удается производить сжатие информации за приемлемое время для сообщений практически любой длины. Особо эффективно применение для данной цели микропроцессорных устройств.

Как задачу нумерации, так и задачу денумерации на основе ОПСС можно эффективно использовать для засекречивания информации. При этом имеется возможность получать помехоустойчивые шифры, обладающие высокой стойкостью и простыми ключами. Особое значение имеет простота и надежность аппаратурной реализации шифрации и дешифрации засекречиваемых сообщений.

Среди комбинаторных задач особое место занимают задачи комбинаторной оптимизации. Причем в самом общем виде указанные задачи могут даже не иметь четко выраженной целевой функции и задаваться, например, в терминах предпочтения. Для таких задач наиболее распространенным решением является перебор возможных вариантов и выбор из него наилучшего по некоторому критерию [2]. В случае, если перебор невозможен, то он заменяется случайным поиском. В том и другом случаях требуется организовать или перебор, или генерирование комбинаторных объектов. ОПСС дают возможность предложить общий метод решения этой задачи.

Таким образом, ОПСС на основе единого подхода дают

возможность эффективно решать ряд практических задач различного характера.

#### Список литературы

- 1. *Стахов А. П.* Коды золотой пропорции.- М.: Радио и связь, 1984. 150 с.

- 2. Стоян Ю. Г., Соколовский В. 3. Решение некоторых многоэкстремальных задач методом сужающихся окрестностей. К.: Наук. думка, 1980. 205 с.

- 3. *Цымбал В. П.* Теория информации и кодирование. К.: Вища шк. Головное изд-во, 1977. 287 с.

- 4. *Кузьмин И. В., Кедрус В. А.* Основы теории информации и кодирования.- К.: Вища шк. Головное изд-во, 1977. 279 с.

### 1.3 Биноминальные системы счисления с двоичным алфавитом

А. А. Борисенко, канд техн. наук, Г. В. Куно

Автоматизированные системы управления и приборы автоматики, Харьков, № 76, 1985 г.

В вычислительной технике широко распространены степенные системы счисления с двоичным алфавитом. Более сложные системы счисления, в которых зависимость между весом разряда и его номером отличается от степенной, менее известны и не нашли практического применения. Однако в дальнейшем выявились полезные свойства некоторых нестепенных систем счисления: помехоустойчивость, генерация и перебор комбинаторных конфигураций, кодирование информации и т. д. [1].

Здесь предлагаются нестепенные системы счисления с биномиальными весами и двоичным алфавитом  $\{1,0\}$  - биномиальные системы счисления [2].

Количественный эквивалент кодовой комбинации n-разрядной k-биномиальной системы счисления  $A_i=(a_{j-1},\,a_{j-2},\,...,\,a_0),\,\,i=0,\,1,...,\,P$ -1 определяется выражением

$$A_i = a_{j-1}C_{n-1}^{r-q_j} + \dots + a_lC_{n-j+l}^{k-q_{l+1}} + \dots + a_0C_{n-j}^{k-q_1}$$

(1)

при соблюдении систем ограничений:

$$\int q_0 = k,$$

(2)

$$j < n, \tag{3}$$

$$\begin{cases} n - k = j - q_0, \\ q_0 < k, \end{cases} \tag{4}$$

где  $q_0$  - число единиц в биномиальном числе;

P - диапазон чисел;

ј - количество разрядов биномиального числа (длина); l - 0, 1, ..., j-1 - порядковые номера разряда;  $q_l$  - сумма единичных значений цифр от (i-1)-го разряда до l-го включительно:

$$q_l = \sum_{i=l}^{j} a_i,$$

$$q_j = a_j = 0.$$

$$q_j = a_j = 0.$$

Система счисления должна удовлетворять требованиям конечности, эффективности, однозначности [3]. Однако этих требований для нестепенных систем счисления недостаточно. Запишем дополнительные требования:

1 Префиксность кодовых комбинаций чисел, позволяющая отличать одни кодовые комбинации от других. По этому требованию любая кодовая комбинация не может быть началом другой.

2 Компактность. Состоит в том, что для каждой кодовой комбинации числа из заданного диапазона существует другая, численное значение которой больше первой на единицу. Исключение делается только для комбинации наибольшего числа.

Из выражения (1) следует, что требования конечности и эффективности для биномиальных систем счисления выполняются, т. е. существует вычислительный алгоритм, который за конечное число шагов осуществляет переход от биномиальной кодовой комбинации

$A_{i}$  ограниченной длины к соответствующему числу.

Докажем, что требование префиксности кодовых комбинаций для биномиальных чисел также удовлетворяется.

Биномиальные кодовые комбинации, удовлетворяющие ограничению (2), должны постоянно содержать k единиц. Поэтому появление в биномиальной комбинации к-й единицы является признаком ее конца. Так как в соответствии с ограничением (3) наибольшая длина указанных комбинаций равна n-1, то их длины принимают значения в пределах от k до n-1 ( $k \le j \le n-1$ ). Соответственно количество содержащихся в них нулей z = 0, 1, ..., n - k - 1, а длина j = k + z. Количество различающихся комбинаций одинаковой длины, содержащих kединиц и нулей, равно числу сочетаний z нулей из j-1 элементов  $C_{k+z-1}^{z}$ . Эти комбинации, являясь сочетаниями, обладают по отношению друг к другу очевидным свойством префиксности. Длины комбинаций, принадлежащие к группам с разным значением z, различны. Так как в конце этих комбинаций стоят единицы и их общее число постоянно и равно k, то более длинные комбинации в префиксной части, равной длине меньшей комбинации, содержат, как минимум, на одну единицу меньше.

Таким образом, против хотя бы одного из нулей меньшей комбинации в префиксной части большей будет стоять единица. Следовательно, свойство префиксности соблюдается для всех комбинаций, удовлетворяющих ограничениям (2) и (3).

Как следует из (4), число нулей в биномиальных комбинациях является постоянным и равным (n-k). Поэтому появление (n-k)-го нуля в комбинации есть признак ее окончания. Сумма (n-k) нулей с числом единиц  $q_0=0,1,...,k-1$  определяет длину  $j=n-k-q_0$  комбинаций. Число различных комбинаций с  $q_0$  единицами и нулем в конце определяется количеством сочетаний  $q_0$  единиц из (j-1) элементов- $C_{n-k+q_0-1}^{q_0}$ . Свойство префиксности для них очевидно. Комбинации, принадлежащие к группам, содержащим разное число единиц, имеют разную длину. При этом меньшие из них, которые могут быть префиксом более длинных, содержат (n-k) нулей. Более длинные также содержат (n-k) нулей, но так как в конце стоит нуль, то их префиксная часть, равная длине меньшей комбинации, содержит, как мини-

мум, на один нуль меньше, что свидетельствует об их префиксности.

Кодовые комбинации рассмотренных выше двух классов также обладают свойством префиксности между собой, так как отличаются числом содержащихся в них единиц и нулей.

Таким образом, среди всех комбинаций, удовлетворяющих ограничениям (2 - 5), отсутствуют комбинации, которые могли бы быть началом других, т. е. свойство префиксности для них соблюдается.

Из свойства префиксности следует, что две произвольные биномиальные комбинации имеют хотя бы в одном разряде различные цифры (0 и 1). Предшествующие этому разряду части комбинации, если они присутствуют, являются для указанных цифр общими, а последующие совместно с ним - собственными. Если собственные части двух произвольных биномиальных комбинаций не могут представлять одно и то же число, то свойство однозначности биномиальной системы счисления будет доказано. Рассмотрим собственные части двух биномиальных комбинаций:

$$A_q = (a_{\alpha},...,a_0)$$

и  $A_z = (a_{\beta},...,a_0)$  ,

где

$$a_{\alpha} = 0 \; , a_{\beta} = 1 \; ; \; q, z = 0, 1, ..., P - 1 \; ; \; \alpha, \beta = 0, 1, ..., n - 1 \; ; \; q \neq z \; .$$

Если допустить, что для комбинации  $A_q$  цифры, следующие за старшим разрядом, равны 1, а в комбинации  $A_z$  - 0, то разность между комбинациями  $A_z$  и  $A_q$  будет минимальной. Докажем, что она не равна нулю.

Представим числа  $A_a$  и  $A_z$  в виде

$$A_q = 0C_{n-j+\alpha}^{k-q_{\alpha+1}} + 1C_{n-j+\alpha-1}^{k-q_{\alpha+1}} + 1C_{n-j+\alpha-2}^{k-q_{\alpha+1}-1} + \dots + 1C_{n-j+\alpha-\alpha}^{k-q_{\alpha+1}-\alpha+1},$$

$$A_z = 1C_{n-j+\beta}^{k-q_{\beta+1}} + 0C_{n-j+\beta-1}^{k-q_{\beta+1}-1} + 0C_{n-j+\beta-2}^{k-q_{\beta+1}-1} + \dots + 0C_{n-j+\beta-\beta}^{k-q_{\beta+1}-1}.$$

Так как

$$\sum_{i=1}^{\alpha} C_{n-j+i-1}^{k-q_{\alpha+1}-\alpha+i} = C_{n-j+\alpha}^{k-q_{\alpha+1}} - 1 = A_q$$

$$C_{n-j+\alpha}^{k-q_{\alpha+1}}=C_{n-j+\beta}^{k-q_{\beta+1}}=A_z$$

, то  $A_z=A_q+1$  .

Следовательно,  $A_q \neq A_z$ , и свойство однозначности для биномиальной системы счисления выполняется.

Максимальное число в биномиальной системе счисления в соответствии с выражением (1)

$$A_{p-1} = 1C_{n-1}^{k-q_j} + 1C_{n-2}^{k-q_j-1} + \dots + 1C_{n-j}^{k-q_1} = C_n^k - 1.$$

Минимальное число равно нулю, а количество биномиальных комбинаций, содержащих в конце единицу,

$$N_1 = \sum_{i=0}^{n-k-1} C_{n-2-i}^{n-k-1-i} = C_{n-1}^{n-k-1} = C_{n-1}^k.$$

Число комбинаций, содержащих в конце нуль,

$$N_0 = \sum_{i=0}^{k-1} C_{n-2-i}^{k-1-i} = C_{n-1}^{k-1}.$$

Их суммарное количество

$$N = C_{n-1}^k + C_{n-1}^{k-1} = C_n^k$$

.

Так как каждой комбинации вследствие свойства однозначности соответствует свое число, при этом минимальное равно 0, а максимальное -  $C_{n-1}^k$  и их количество равно  $C_n^k$ , то требование компактности для биномиальной системы счисления удовлетворяется. Соответственно диапазон представимых чисел  $P=C_n^k$ .

В табл. 1 для n = 6 и k = 4 приведены биномиальные комбинации и их количественные эквиваленты, формирование которых осуществ-

ляется по следующему алгоритму:

- 1 Формируется начальная комбинация, состоящая из (n-k) нулей.

- 2 В младший разряд записывается единица и к нему справа приписывается нуль.

- 3 Пункт 2 повторяется до тех пор, пока число единиц в кодовом слове не станет равным k. В этом случае приписывание нуля справа не происходит.

- 4 В младший разряд, содержащий нуль, записывается 1.

- 5 Определяется число единиц в комбинации. Если оно равно k и единицы не занимают k старших разрядов, то происходит возврат к пункту 4.

- 6 Если k единиц занимают в комбинации k старших разрядов, то происходит останов.

- 7 Если число единиц в комбинации не равно k, то справа от младшего разряда, содержащего 1, записываются нули до тех пор, пока их общее число не станет равным (n-k).

- 8 Возврат к пункту 2.

Таблица 1

| Биномиаль- | Количественный эквивалент                    |

|------------|----------------------------------------------|

| 00         | $0C_5^4 + 0C_4^4$                            |

| 010        | $0C_5^4 + 1C_4^4 + 0C_3^3$                   |

| 0110       | $0C_5^4 + 1C_4^4 + 1C_3^3 + 0C_2^2$          |

| 01110      | $0C_5^4 + 1C_4^4 + 1C_3^3 + 1C_2^2 + 0C_1^1$ |

| 01111      | $0C_5^4 + 1C_4^4 + 1C_3^3 + 1C_2^2 + 1C_1^1$ |

| 100        | $1 C_5^4 + 0 C_4^3 + 0 C_3^3$                |

| 1010       | $1C_5^4 + 0C_4^3 + 1C_3^3 + 0C_2^2$          |

| 10110      | $1C_5^4 + 0C_4^3 + 1C_3^3 + 1C_2^2 + 0C_1^1$ |

| 10111      | $1C_5^4 + 0C_4^3 + 1C_3^3 + 1C_2^2 + 1C_1^1$ |

| 1100       | $1C_5^4 + 1C_4^3 + 0C_3^2 + 0C_2^2$          |

| 11010 | $1C_5^4 + 0C_4^3 + 0C_3^2 + 1C_2^2 + 0C_1^1$ |

|-------|----------------------------------------------|

| 11011 | $1C_5^4 + 1C_4^3 + 0C_3^2 + 1C_2^2 + 1C_1^1$ |

| 11100 | $1C_5^4 + 1C_4^3 + 1C_3^2 + 0C_2^1 + 0C_1^1$ |

| 11101 | $1C_5^4 + 1C_4^3 + 1C_3^2 + 0C_2^1 + 1C_1^1$ |

| 1111  | $1C_5^4 + 1C_4^3 + 1C_3^2 + 1C_2^1$          |

Полезными свойствами биномиальной системы счисления являются: помехоустойчивость при передаче, хранении и обработке информации; способность перебирать, генерировать и нумеровать комбинации кодов с постоянным весом; возможность построения помехоустойчивых цифровых устройств.

Для обнаружения ошибок с помощью биномиальных комбинаций необходимо дополнить их нулями или единицами до получения равномерного (n-1)-разрядного биномиального кода, как это привелено в табл. 2.

Таблица 2

| Пор. | Биномиальный<br>код | Биномиальный равномерный код | Пор. | Биномиальный<br>код | Биномиальный равномерный код |

|------|---------------------|------------------------------|------|---------------------|------------------------------|

| 0    | 00                  | 00000                        | 8    | 10111               | 10111                        |

| 1    | 010                 | 01000                        | 9    | 1100                | 11000                        |

| 2    | 0110                | 01100                        | 10   | 11010               | 11010                        |

| 3    | 01110               | 01110                        | 11   | 11011               | 11011                        |

| 4    | 01111               | 01111                        | 12   | 11100               | 11100                        |

| 5    | 100                 | 10000                        | 13   | 11101               | 11101                        |

| 6    | 1010                | 10100                        | 14   | 1111                | 11110                        |

| 7    | 10110               | 10110                        |      |                     |                              |

Основными признаками ошибки в биномиальной комбинации в первом случае является превышение числа единиц в ней величины k, во втором - числа (n-k) нулей. Особым свойством биномиального помехоустойчивого кода является его способность обнаруживать ошибки при обработке информации. Это позволяет организовать сквозной контроль в каналах обработки информации, в которые входят и цифровые устройства. Одно из таких устройств предложено в

работе [4].

В табл. 3 приведен переход от биномиальной комбинации к коду с постоянным весом, который осуществляется приписыванием к комбинации единиц, если она содержит (n - k) нулей, или нулей, если в ней содержится k единиц, до тех пор, пока ее длина не станет равной n.

Биномиальная комбинация является биномиальным номером комбинации с постоянным весом, т. е. является ее сжатым отображением. Если есть необходимость представить ее номером в степенной системе счисления, то тогда необходимо воспользоваться выражением (1).

Алгоритмы перебора и генерирования биномиальных комбинаций и на их основе комбинаций с постоянным весом более подробно рассмотрены в работе [5].

| Tr ~    | $^{\circ}$ |

|---------|------------|

| Таблица | 4          |

| таолица | J          |

| 1 4031 | тиолици 3           |                                       |              |                     |                                       |  |  |  |  |

|--------|---------------------|---------------------------------------|--------------|---------------------|---------------------------------------|--|--|--|--|

| Пор.   | Биномиальный<br>код | Биномиальный код с постоян- ным весом | Пор.<br>ном. | Биномиальный<br>код | Биномиальный код с постоян- ным весом |  |  |  |  |

| 0      | 00                  | 001111                                | 8            | 10111               | 101110                                |  |  |  |  |

| 1      | 010                 | 010111                                | 9            | 1100                | 110011                                |  |  |  |  |

| 2      | 0110                | 011011                                | 10           | 11010               | 110101                                |  |  |  |  |

| 3      | 01110               | 011101                                | 11           | 11011               | 110110                                |  |  |  |  |

| 4      | 01111               | 011110                                | 12           | 11100               | 111001                                |  |  |  |  |

| 5      | 100                 | 100111                                | 13           | 11101               | 111010                                |  |  |  |  |

| 6      | 1010                | 101011                                | 14           | 1111                | 111100                                |  |  |  |  |

| 7      | 10110               | 101101                                |              |                     | ·                                     |  |  |  |  |

Таким образом, предложенная биномиальная система счисления способна осуществлять сквозной контроль канала преобразования информации и позволяет перебирать, генерировать и нумеровать комбинации кодов с постоянным весом.

### Список литературы

- 1. Стахов А П. Фибоначиевы двоичные позиционные системы счисления: Кодирование и передача дискретных сообщений в системах связи. М.: Наука, 1976. 179 с.

- 2. *Борисенко А. А.* Система счисления с биномиальным основанием и двоичным алфавитом. Деп. в ВИНИТИ 29.08.82., № 909 82. 6 с.

- 3. *Поспелов Д. Н.* Арифметические основы вычислительных машин дискретного действия. М.: Высш. шк., 1970. 308 с.

- 4. А. с. 1077054. Счетчик импульсов / А. А. Борисенко, И. Д. Пузько, Л.А. Стеценко.

- 5. Борисенко А. А., Губарев С. И., Куно Г. В. Алгоритмы построения кодов с постоянным весом на основе биномиальных чисел // АСУ и приборы автоматики, 1985.- Вып. 74. С. 31 35.

# 1.4 Алгоритмы помехоустойчивого биноминального двоичного счета

А. А. Борисенко, канд. техн. наук, Г. В. Куно

Автоматизированные системы управления и приборы автоматики, Харьков, № 82, 1987 г.

Рассматриваемые в данной работе алгоритмы работают в биномиальной двоичной системе счисления [1] и предназначены для помехоустойчивого биномиального счета. Их применение целесообразно в системах телеавтоматики со сквозным контролем ошибок, в специализированных помехоустойчивых преобразователях информации, в генераторах и нумераторах сочетаний. На их основе возможна реализация помехоустойчивых счетчиков со взвешенными кодами.

Кодовая комбинация k - биномиальной системы счисления с двоичным алфавитом длины  $A_i=(a_{j-1},\,a_{j-2},\,...,\,a_0),\,i=0,\,1,\,...,\,P\text{-}1$  определяется выражением

$$A_{i} = a_{j-1}C_{n-1}^{k-q_{i}} + a_{l}C_{n-j+l}^{k-q_{i+1}} + \dots + a_{0}C_{n-j}^{k-q_{1}}$$

$$\tag{1}$$

при соблюдении ограничений:

$$q_0 = k (2)$$

$$j < n (3)$$

$$n - k = j - q , (4)$$

$$q_0 < k \,, \tag{5}$$

$$1 \le k \le n \,, \tag{6}$$

где  $P = C_n^k$  - диапазон представимых чисел;

n - количество разрядов биномиального числа;

$q_0$  - сумма единичных значений цифр от (j-1)-го разряда до l-го включительно:

$$q_l = \sum_{i=1}^j a_j ,$$

$$q_j = a_j = 0,$$

где l = 0,1,..., j-1 - порядковый номер разряда;

k - контрольное число, определяющее допустимое число единиц в кодовой комбинации; n=P+1.

Ограничения (2), (3), (4), (5) показывают, что длина j биномиальных чисел находится в пределах n -  $k \le j \le n-1$ , и биномиальное число содержит или k единиц, или n-k нулей. Причем в первом случае это число в конце содержит 1, а во втором - 0. Комбинация, в которой приведенные условия нарушены, является ошибочной. Например, комбинации 00, 01111, 0110 при n=6, k=4 являются биномиальными, так как первая и третья содержат по 2 нуля, а вторая - 4 единицы, причем в 1-й и 3-й комбинациях в конце стоит 0, а во второй - 1. Комбинация 00111 является ошибочной, так как хотя и содержит 2 нуля, но заканчивается 1.

Указанные ограничения совместно с выражением (1) приводят к следующему алгоритму счета биномиальных чисел:

- 1 Формируется начальная кодовая комбинация, состоящая из n-k нулей.

- 2 В младший разряд, стоящий в конце комбинации справа и содержащий нуль, записывается 1.

- 3 Подсчитывается число единиц в полученной кодовой комбинации. Если оно равно k, то переход к пункту 5.

- 4 Если оно не равно k, то справа от содержащего 1 младшего разряда записывается нуль. Результатом является следующая по порядку биномиальная кодовая комбинация. Возврат к пункту 2.

- 5 Если число единиц в кодовой комбинации равно k и единицы не расположены в k старших разрядах, то младшие нулевые преобра-

зовываются в 1, все остальные, идущие после него единицы, преобразуются в нули. Переход к пункту 3.

6 Если число единиц равно k и единицы расположены в k старших разрядах, то получена последняя биномиальная комбинация из лиапазона P.

В соответствии с приведенным алгоритмом в табл. 1 получены состояния 5-разрядного 4-биномиального счетчика и их количественные эквиваленты. Число его состояний  $P = C_n^k = 15$ .

Приведенный алгоритм является основой биномиальных счетчиков, конкретная структура которых может быть задана в виде программы для универсальной ЭЦВМ, микропроцессорного устройства, а также устройства с жесткой логикой, собранного из отдельных элементов или изготовленного в виде интегральной схемы.

Использование программы биномиального счета в универсальных ЭЦВМ имеет практическое значение в случае помехоустойчивого кодирования данных или если стоит задача перебора, генерирования или нумерации сочетаний. Такая программа была разработана и испытана авторами.

Микропроцессорный вариант биномиального счетчика целесообразен в специализированных цифровых устройствах со сквозным контролем обрабатываемой информации при относительно невысоких требованиях к их быстродействию.

Биномиальные счетчики с жесткой логикой могут найти применение как в специализированных, так и в универсальных цифровых устройствах. Наличие таблиц функционирования биномиальных счетчиков, аналогичных табл. 1, позволяет производить их структурный синтез и получить рациональную в смысле минимизации количества элементов структуру счетчика. Однако этот путь сопряжен с усложнением связей между элементами счетчика, что приводит к уменьшению его надежности и быстродействия, потери однородности структуры, сложности перестройки коэффициента пересчета, и поэтому может быть рекомендован там, где вопрос экономии элементов является первостепенным.

Структура счетчика, в определенной мере лишенная указанных недостатков, рассмотрена в [2]. Его состояния получаются из исходных (табл. 1) путем дополнения кодовых комбинаций нулями до длины n-1 (табл. 2).

Соответственно приведенный выше алгоритм счета преобразуется к виду:

- 1 В исходном состоянии все разряды счетчика установлены в нуль.

- 2 Заносится 1 в (k-i-1)-й разряд, где i число единиц в счетчике.

- 3 Если число единиц в счетчике больше k, то произошла ощибка.

- 4 Если число единиц в счетчике равно k и они не расположены в k старших разрядах, то все младшие единичные разряды до первого нулевого устанавливаются в 0, а первый нулевой в 1.

- 5 Если число единиц в счетчике меньше k, то происходит переход к пункту 2.

- 6 Если число единиц в счетчике равно k и они расположены в k старших разрядах, то цикл счета окончен. Возврат к пункту 1.

Таблица 1

| таоли.    | ца і                  |                                                                                 |

|-----------|-----------------------|---------------------------------------------------------------------------------|

| Пор. ном. | Биномиальное<br>число | Количественный эквивалент                                                       |

| 0         | 00                    | $0 \cdot C_5^4 + 0 \cdot C_4^4$                                                 |

| 1         | 010                   | $0 \cdot C_5^4 + 1 \cdot C_4^4 + 0 \cdot C_3^3$                                 |

| 2         | 0110                  | $0 \cdot C_5^4 + 1 \cdot C_4^4 + 1 \cdot C_3^3 + 0 \cdot C_2^2$                 |

| 3         | 01110                 | $0 \cdot C_5^4 + 1 \cdot C_4^4 + 1 \cdot C_3^3 + 1 \cdot C_2^2 + 0 \cdot C_1^1$ |

| 4         | 01111                 | $0 \cdot C_5^4 + 1 \cdot C_4^4 + 1 \cdot C_3^3 + 1 \cdot C_2^2 + 1 \cdot C_1^1$ |

| 5         | 100                   | $1 \cdot C_5^4 + 0 \cdot C_4^3 + 0 \cdot C_3^3$                                 |

| 6         | 1010                  | $1 \cdot C_5^4 + 0 \cdot C_4^3 + 1 \cdot C_3^3 + 0 \cdot C_2^2$                 |

| 7         | 10110                 | $1 \cdot C_5^4 + 0 \cdot C_4^3 + 1 \cdot C_3^3 + 1 \cdot C_2^2 + 0 \cdot C_1^1$ |

| 8         | 10111                 | $1 \cdot C_5^4 + 0 \cdot C_4^3 + 1 \cdot C_3^3 + 1 \cdot C_2^2 + 1 \cdot C_1^1$ |

| 9         | 1100                  | $1 \cdot C_5^4 + 1 \cdot C_4^3 + 0 \cdot C_3^2 + 0 \cdot C_2^2$                 |

| 10        | 11010                 | $1 \cdot C_5^4 + 1 \cdot C_4^3 + 0 \cdot C_3^2 + 1 \cdot C_2^2 + 0 \cdot C_1^1$ |

| 11 | 11011 | $1 \cdot C_5^4 + 1 \cdot C_4^3 + 0 \cdot C_3^2 + 1 \cdot C_2^2 + 1 \cdot C_1^1$ |

|----|-------|---------------------------------------------------------------------------------|

| 12 | 11100 | $1 \cdot C_5^4 + 1 \cdot C_4^3 + 1 \cdot C_3^2 + 0 \cdot C_2^1 + 0 \cdot C_1^1$ |

| 13 | 11101 | $1 \cdot C_5^4 + 1 \cdot C_4^3 + 1 \cdot C_3^2 + 0 \cdot C_2^1 + 1 \cdot C_1^1$ |

| 14 | 1111  | $1 \cdot C_5^4 + 1 \cdot C_4^3 + 1 \cdot C_3^2 + 1 \cdot C_2^1$                 |

Таблипа 2

| Пор. | Разряд | Пор. | Разряд | Пор. | Разряд | Пор. | Разряд |

|------|--------|------|--------|------|--------|------|--------|

| ном. | 43210  | ном. | 43210  | ном. | 43210  | ном. | 43210  |

| 0    | 00000  | 4    | 01111  | 8    | 10111  | 12   | 11100  |

| 1    | 01000  | 5    | 10000  | 9    | 11000  | 13   | 11101  |

| 2    | 01100  | 6    | 10100  | 10   | 11010  | 14   | 11110  |

| 3    | 01110  | 7    | 10110  | 11   | 11011  |      |        |

Ошибки в счетчике обнаруживаются при превышении количества единиц в его разрядах величины k. Тип ошибок  $0 \rightarrow 1$ . В рассматриваемом примере счетчика с k=4 обнаруживаемым ошибочным состоянием будет 11111. Любая четырехкратная ошибка в нем будет замечена. В то же время однократная ошибка указанного вида будет индицироваться для 30 % (5) комбинаций: 01111, 10111, 11011, 11101, 11110. Если учесть, что ошибки в счетчиках возникают преимущественно в виде пакетов и носят характер  $0 \rightarrow 1$ , то его способность к обнаружению ошибок для ряда применений можно считать вполне удовлетворительной. Ее можно значительно увеличить, уменьшив k и соответственно - коэффициент пересчета. При условии, что k=1, любые ошибки типа  $0 \rightarrow 1$  будут обнаружены, а сам счетчик преобразуется в помехоустойчивый распределитель импульсов.

В случае необходимости обнаруживать ошибки типа  $1 \to 0$  в счетчик необходимо ввести дополнительные элементы, учитывающие ограничения (4, 5), в соответствии с которыми биномиальная комбинация может содержать не более n-k нулей, последний из которых должен быть в конце. Поэтому если перед последней единицей в комбинации табл. 2 находится n-k и более нулей, то произошла ошибка типа  $1 \to 0$ . Так, например, комбинация 00110 будет воспринята как

ошибочная. Причем с ростом k обнаруживающая способность счетчика к ошибкам  $1 \to 0$  растет. При k = n - 1 любой переход  $1 \to 0$ , за исключением сбоя последней единицы комбинации, будет обнаружен. Это позволяет изменением коэффициента пересчета счетчика настраивать его на определенный характер помех, т. е. производить адаптацию к ним.

В основу решения задачи алгоритма счета при вычитании в биномиальной системе счисления с заданными k и n положен рассмотренный выше алгоритм сложения. Алгоритм вычитания состоит из следующих двух этапов:

- 1 Происходит счет биномиальных чисел по алгоритму сложения, начиная с нуля, с контрольным числом k'=n-k.

- 2 Разряды каждой полученной в процессе счета комбинации инвертируются до k-го нуля или k' единицы включительно, считая со старшего разряда.

Для примера в табл. 3 приведены последовательности состояний счетчиков суммирующего с k=4 и k'=2 и вычитающего с k=4 .

Таблица 3

|              | Состоя                 | ние счетчи                        | ка                      | $\mathcal{Q}^{\mathcal{T}}$ | Состояние счетчика                |                                   |                                   |  |

|--------------|------------------------|-----------------------------------|-------------------------|-----------------------------|-----------------------------------|-----------------------------------|-----------------------------------|--|

| Пор.<br>ном. | при сложении $c k = 4$ | при<br>сложении<br>с <i>k</i> = 2 | при вычитании $c k = 4$ | Пор.                        | при<br>сложении<br>с <i>k</i> = 4 | при<br>сложении<br>с <i>k</i> = 2 | при<br>вычитании<br>с <i>k</i> =4 |  |

| 0            | 00000                  | 00000                             | 11110                   | 8                           | 10111                             | 01010                             | 10100                             |  |

| 1            | 01000                  | 00010                             | 11101                   | 9                           | 11000                             | 01100                             | 10000                             |  |

| 2            | 01100                  | 00011                             | 11100                   | 10                          | 11010                             | 10000                             | 01111                             |  |

| 3            | 01110                  | 00100                             | 11011                   | 11                          | 11011                             | 10001                             | 01110                             |  |

| 4            | 01111                  | 00101                             | 11010                   | 12                          | 11100                             | 10010                             | 01100                             |  |

| 5            | 10000                  | 00110                             | 11000                   | 13                          | 11101                             | 10100                             | 01000                             |  |

| 6            | 10100                  | 01000                             | 10111                   | 14                          | 11110                             | 11000                             | 00000                             |  |

| 7            | 10110                  | 01001                             | 10110                   |                             | · ·                               | ·                                 |                                   |  |

Алгоритмы биномиального счета прошли программную и аппаратную опытную проверку. Результаты испытаний биномиального счетчика с n=5 при значениях k от 1 до 5 подтвердили его работоспособность и эффективность.

#### Список литературы

- 1. *Борисенко А. А.* Система с биномиальным основанием и двоичным алфавитом. Деп. в ВИНИТИ 19.09.82, № 909 82. С. 6.

- $2.\ A.\ c.\ 1077054$ . Счетчик импульсов / А. А. Борисенко, И. Д. Пузько, Л. А. Стеценко.

#### 1.5 Биноминальные счетчики

А. А. Борисенко, канд. техн. наук, С. И. Губарев, канд. техн. наук,  $\Gamma$ . В. Куно

Автоматизированные системы управления и приборы автоматики, Харьков, № 92, 1989 г.

Имеются две основные тенденции в развитии средств обработки данных - применение микропроцессоров и создание достаточно полного набора микроэлектронных устройств, реализующих наиболее распространенные вычислительные операции. Первая предусматривает программный, вторая - схемотехнический способ реализации вычислительных функций. Схемная реализация средств обработки данных по сравнению с программной во много раз повышает скорость выполнения операций и незаменима в устройствах управления, работающих в реальном масштабе времени.

Особое место среди схем, применяемых для обработки данных, занимают счетчики. Счет является важнейшей частью в организационных и технологических автоматизированных системах управления. Счетчики важны не только сами по себе, но и с точки зрения новых схемотехнических решений в области цифровых устройств, так как к ним можно отнести любое устройство, которое в процессе работы проходит через несколько состояний [1].

Широкое применение счетчиков требует повышения их надежности, в частности, помехоустойчивости. Последнее достигается введением в счетчики запрещенных состояний. Однако их обнаружение выливается подчас в довольно сложную задачу и требует разработки дополнительно к счетчику контролирующего устройства, за правильностью работы которого необходимо следить. Счетчик при этом приобретает неоднородную структуру, которую непросто проектировать и отладить, а его надежность может даже снизиться.

Преодолеть указанные противоречия можно путем применения

помехоустойчивых систем счисления. Разработанные на их основе счетчики однородны и помехоустойчивы. Они не содержат специального контролирующего устройства, хотя избыточность аппаратуры по сравнению с двоичными счетчиками у них все же имеется.

К этому классу устройств принадлежат и биномиальные счетчики, работающие в биномиальной системе счисления [2]. Важной их особенностью является значительное уменьшение аппаратуры, необходимой для дешифрации их состояний. В ряде случаев это может привести к тому, что количество аппаратурных затрат в устройстве с биномиальными счетчиками в целом уменьшится по сравнению с устройством, содержащим двоичные счетчики. Кроме того, эти счетчики позволяют изменением коэффициента пересчета адаптироваться к интенсивности и характеру помех.

Вторым немаловажным, если не основным, достоинством счетчиков, работающих в помехоустойчивых системах счисления, является возможность перебирать комбинаторные конфигурации, например, сочетания, сочетания с повторениями, перестановки и т. д. Таким образом, счетчики помехоустойчивых систем счисления обладают немаловажными достоинствами - помехоустойчивостью и многофункциональностью.

Рассмотрим работу одного из биномиальных счетчиков [3]. Он характеризуется двумя основными параметрами - числом разрядов n и контрольным числом k. При этом смена состояний биномиального счетчика происходит по следующим правилам: в исходном состоянии все разряды счетчика установлены в нуль; заносится единица в (k - i)-й разряд, где i - число единиц в счетчике; если число единиц в счетчике равно k и они не расположены в k старших разрядах, то младшие единичные разряды до первого старшего нулевого устанавливаются в нуль, а первый старший нулевой - в единицу; если число единиц в счетчике равно k и они расположены в k старших разрядах, то цикл счета окончен. Возврат к началу.

Число состояний счетчика определяется числом сочетаний единиц из (n+1) элементов:

$$N = C_{n+1}^k = \frac{(n+1)!}{k!(n-k+1)!}.$$

Состояния счетчика для k=2 и k=4 для числа разрядов n=5 в

порядке возрастания приведены в табл. 1 и 2. Их число  $C_6^2 = C_6^4 = 15$  .

| • | _ ،    | 1   |

|---|--------|-----|

| 1 | аблица | - 1 |

| 1 | аолица | 1   |

| Пор. | Разряд          | Пор. | Разряд    | Пор. | Разряд    | Пор. | Разряд    |

|------|-----------------|------|-----------|------|-----------|------|-----------|

| ном. | 5 4 3 2 1       | ном. | 5 4 3 2 1 | ном. | 5 4 3 2 1 | ном. | 5 3 3 2 1 |

| 0    | $0\ 0\ 0\ 0\ 0$ | 4    | 00101     | 8    | 01010     | 12   | 10010     |

| 1    | 00010           | 5    | 00110     | 9    | 01100     | 13   | 10100     |

| 2    | 00011           | 6    | 01000     | 10   | 10000     | 14   | 11000     |

| 3    | 00100           | 7    | 0 1 0 0 1 | 11   | 10001     |      |           |

#### Таблица 2

| Пор. | Разряд    | Пор. | Разряд    | Пор. | Разряд    | Пор. | Разряд    |

|------|-----------|------|-----------|------|-----------|------|-----------|

| ном. | 5 4 3 2 1 |

| 0    | 00000     | 4    | 01111     | 8    | 10111     | 12   | 11100     |

| 1    | 01000     | 5    | 10000     | 9    | 1 1 0 0 0 | 13   | 11101     |

| 2    | 01100     | 6    | 10100     | 10   | 11010     | 14   | 11110     |

| 3    | 01110     | 7    | 10110     | 11   | 11011     |      |           |

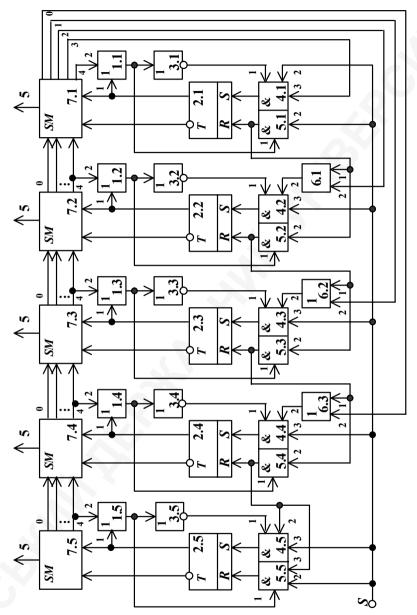

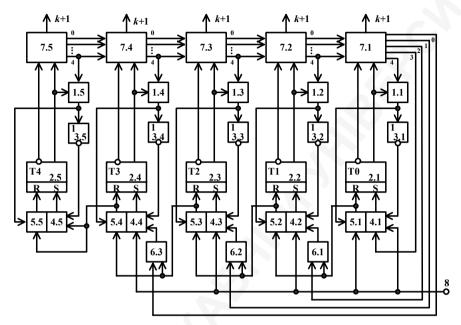

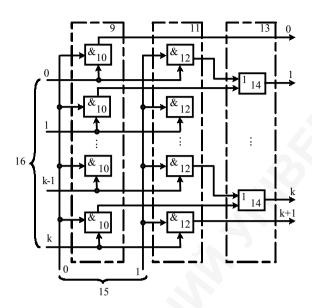

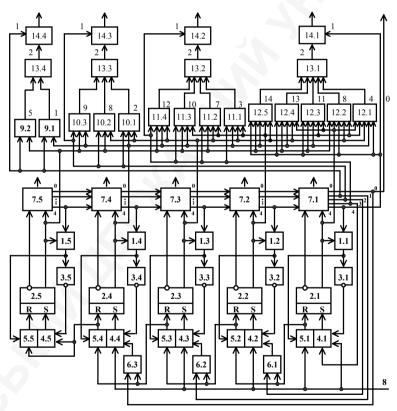

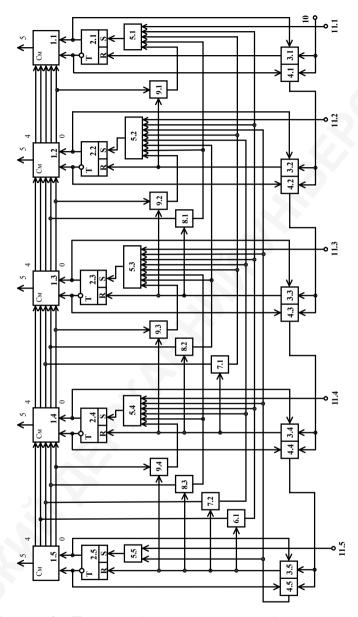

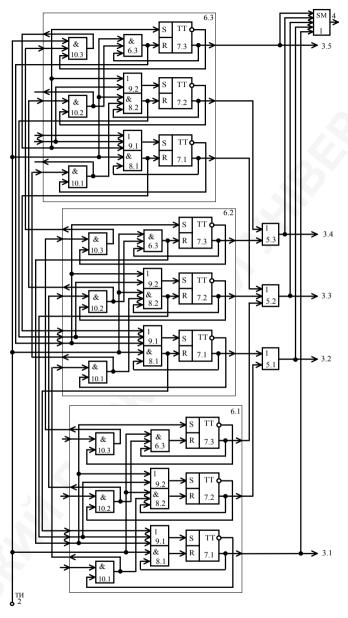

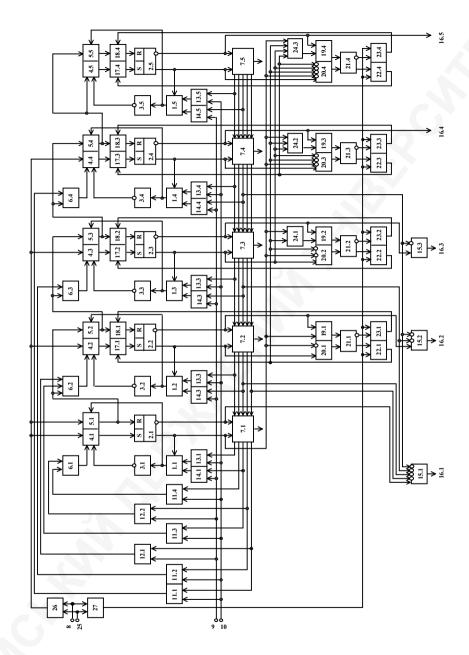

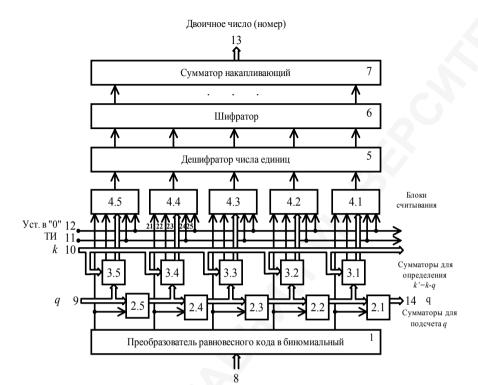

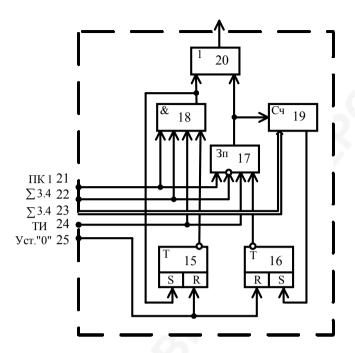

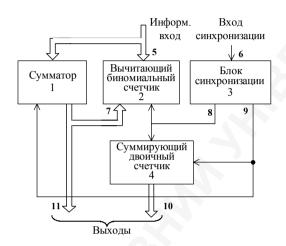

Работа биномиального счетчика заключается в следующем (см. рис. 1). Его исходным состоянием является нулевое. Поэтому на нулевом выходе сумматора младшего разряда счетчика находится единичный сигнал, который через схему ИЛИ 6.3 приходит на второй вход схемы И 4.4. Если на четвертом выходе сумматора 7.4 находится нулевой сигнал, то на первый вход схемы И 4.4 при этом приходит единичный разрешающий сигнал. Поэтому триггер Т 2.4 устанавливается в единичное состояние тактовым сигналом, приходящим на третий вход схемы И 4.4. В результате на первом выходе сумматора 7.1 появится единичный сигнал, который откроет схему И 4.3 и запишет в триггер Т 2.3 единицу. Таким образом, счет единиц продолжается, пока их количество в счетчике не станет равным четырем.

Появление на четвертом выходе любого сумматора, например 7.1, единичного сигнала приводит к закрытию схем И 4 и открыванию схем И 5 (для младшего разряда это схемы И 4.1, И 5.1), что приводит к установке соответствующих триггеров в нулевое состояние по тактовому импульсу. При этом в ноль сбрасывается не только триггер, сумматор которого содержит единицу на четвертом выходе, а и соседний, не имеющий таковой единицы. Это достигается соединением

единичных выходов триггеров с первыми входами схем ИЛИ 1.

Если счетчик в результате одиночной ошибки или пакета ошибок  $0 \rightarrow 1$  перейдет в состояние 11111, т. е. будет содержать k+1 единицу, то на пятом выходе сумматора младшего разряда вырабатывается сигнал ошибки. Обнаруживающая способность счетчика для ошибок  $0 \rightarrow 1$  возрастает с уменьшением контрольного числа k и достигает максимального значения при k=1.

Особенностью рассматриваемого счетчика является наличие комбинационных матричных сумматоров, которые выполняют функции переноса и схем контроля и в обычных счетчиках отсутствуют. Кроме того, они в значительной степени выполняют функции дешифратора. Поэтому дешифрация состояний биномиального счетчика значительно упрощается. Важными достоинствами рассматриваемого счетчика являются его однородность и возможность простой перестройки коэффициента пересчета и соответственно степени помехоустойчивости.

Наиболее перспективно применение биномиальных счетчиков в специализированных помехоустойчивых устройствах автоматики и телемеханики в качестве надежных распределителей импульсов, пересчетных схем, кодирующих и декодирующих устройств. Практические испытания биномиальных счетчиков в условиях, приближенных к производственным, подтвердили их работоспособность и эффективность.

### Список литературы

- 1. Оберман Р. М. Счет и счетчики. М., 1984. 173 с.

- 2. Борисенко А. А., Губарев С. И., Куно Г. В. Биномиальные системы счисления с двоичным алфавитом // АСУ и приборы автоматики. 1985. Вып. 76. С. 81- 87.

- 3. А. с. 1077054 . Счетчик импульсов / А. А. Борисенко, И. Д. Пузько, Л. А. Стеценко.

Рисунок 1 - Схема биномиального счетчика для n=5 и k=4

# 1.6 Алгоритмы построения кодов с постоянным весом на основе биноминальных чисел

A.A. Борисенко, канд. техн. наук, C.И. Губарев, канд. техн. наук,  $\Gamma$ . B. Куно

Автоматизированные системы управления и приборы автоматики, Харьков, № 74, 1985 г.

При помехоустойчивом кодировании широко применяются коды с постоянным весом. Их положительные свойства - относительно высокая помехоустойчивость и простота технической реализации [1]. В работе [2] отмечено, что ограничивающим фактором, позволяющим в полной мере реализовать достоинства этих кодов, является отсутствие регулярных методов их построения. Решить такую задачу мы предлагаем на основе применения двоичных биномиальных чисел

$$A_i = (a_{i-1}, a_{i-2}, ..., a_0),$$

где i = 1, 2, ..., P; j - количество разрядов биномиального числа. Эти числа могут быть получены с помощью биномиальных систем счисления с двоичным алфавитом [3].

Диапазон представления биномиальных чисел

$$P = C_n^k$$

,

где k, n - целочисленные параметры системы счисления; k > 0. n > k:

п-разрядность биномиальных чисел;

k - контрольное число.

Биномиальные числа характеризуются следующими признаками: длина j их не должна быть больше n-1 и меньше l=n-k разрядов; биномиальное число должно содержать или k единиц, или l нулей.

Пусть, например, заданы двоичные последовательности 0000, 00, 01111, 1000. Требуется определить, какие из указанных последовательностей при n=6, k=4 являются биномиальными числами, вычислить их диапазон и преобразовать в десятичную систему счисления. Диапазон представления биномиальных чисел для указанных n и k

$P=C_n^k=C_6^4=15$ . Последовательность 0000 не содержит единиц и содержит нулей больше l, поэтому для заданных n и k она не является биномиальным числом. Последовательности 00, 01111 биномиальные, так как в первой число нулей равно l, а во второй число единиц равно k. При этом их длина не превышает n-1=5 и не меньше n-k=2 разрядов.

Переход от биномиального числа к двоичному кодовому слову с постоянным весом осуществляется приписыванием к нему единиц, если двоичное число содержит l нулей, или нулей, если в нем содержится k единиц, до тех пор, пока длина двоичного слова не станет равной n. Например, 00, 001111, 01111, 011110. Правило обратного перехода состоит в вычеркивании из кодового слова с постоянным весом единиц или нулей, начиная с младшего разряда, до тех пор, пока их число не станет равным k или l. Например, 011110 - 011111, 0011111 - 00.

Для решения задачи перебора кодов с постоянным весом рассмотрим алгоритм перебора биномиальных чисел, который основывается на реализации операции сложения биномиального числа с единицей до получения максимального числа  $C_n^k - 1$ , т. е. необходимо разработать алгоритм работы биномиального счетчика.

Этот алгоритм состоит в следующем:

- 1 Формируется начальное кодовое слово, состоящее из нулей.

- 2 В младший разряд записывается единица.

- 3 Если число единиц в кодовом слове меньше k, то приписываем справа нуль и переходим к пункту 2.

- 4 Если число единиц станет равным k, а длина- n 1 разрядов, то в младший разряд, содержащий нуль, записывается единица; а в разряды справа от него, если число единиц слева не равно k, последовательно записываются нули до тех пор, пока их общее число не станет равным n k.

- 5 Возврат к пункту 2.

Циклы повторяются до тех пор, пока k старших разрядов кодового слова не заполнятся единицами.

В табл. 1 для n=6, k=4 приведены все состояния биномиального счетчика, расположенные в порядке возрастания и полученные в соответствии с приведенным алгоритмом.

Таблина 1

|      | Биномиальное |      |       |      |       |      |       |

|------|--------------|------|-------|------|-------|------|-------|

| HOM. | число        | ном. | число | HOM. | число | ном. | число |

| 0    | 00           | 4    | 01111 | 8    | 10111 | 12   | 11100 |

| 1    | 010          | 5    | 100   | 9    | 1100  | 13   | 11101 |

| 2    | 0110         | 6    | 1010  | 10   | 11010 | 14   | 1111  |

| 3    | 01110        | 7    | 10110 | 11   | 11011 |      |       |

Перебор кодов с постоянным весом осуществляется на основе перебора биномиальных чисел, который рассмотрен выше.

Представляет интерес также задача перебора биномиальных чисел и соответственно кодов с постоянным весом в порядке убывания (алгоритм работы вычитающего счетчика). Алгоритм вычитания состоит в присвоении k значения l и инвертировании разрядов в суммирующем счетчике с новым k.

В табл. 2 приведены двоичные последовательности вычитаю-

Таблица 2

| Пор.    | Биномиальные числа | Биномиальные числа | Биномиальные числа вычитающего счетчика |  |  |

|---------|--------------------|--------------------|-----------------------------------------|--|--|

| ном.    | суммирующего       | суммирующего       |                                         |  |  |

| 1101111 | счетчика           | счетчика с $k = l$ |                                         |  |  |

| 0       | 00                 | 0000               | 1111                                    |  |  |

| 1       | 010                | 00010              | 11101                                   |  |  |

| 2       | 0110               | 00011              | 11100                                   |  |  |

| 3       | 01110              | 00100              | 11011                                   |  |  |

| 4       | 01111              | 00101              | 11010                                   |  |  |

| 5       | 100                | 0011               | 1100                                    |  |  |

| 6       | 1010               | 01000              | 10111                                   |  |  |

| 7       | 10110              | 01001              | 10110                                   |  |  |

| 8       | 10111              | 0101               | 1010                                    |  |  |

| 9       | 1100               | 011                | 100                                     |  |  |

| 10      | 11010              | 10000              | 01111                                   |  |  |

| 11      | 11011              | 10001              | 01110                                   |  |  |

| 12      | 11100              | 1001               | 0110                                    |  |  |

| 13      | 11101              | 101                | 010                                     |  |  |

| 14      | 1111               | 11                 | 00                                      |  |  |

На основе приведенных алгоритмов можно решить задачу генерирования кодов с постоянным весом по заданным номерам. Ее решение заключается в одновременном переборе чисел в степенной, например, двоичной и биномиальной системах счисления. При совпадении одного из перебираемых двоичных чисел с заданным происходит одновременный останов перебора двоичных и биномиальных чисел, результат генерирования будет отображен на биномиальном счетчике.

Это решение представляет интерес вследствие возможности его относительно простой схемной реализации. Недостаток его состоит в низкой скорости преобразования, что приводит к принципиальному ограничению на длину генерируемых кодовых комбинаций. Повысить скорость можно на основе приведенного ниже алгоритма перевода чисел из степенной системы счисления в биномиальную:

1 Определяется коэффициент  $a_{j-1}$  сравнением переводимого числа  $A_i$  с весом (j-1)-го разряда  $C_{n-1}^{k-q_j}$ , где  $q_j=0$ . Если  $A_i \geq C_{n-1}^{k-q_j}$ , то  $a_{j-1}=1$ ,  $q_{j-1}=q_j+1=1$ . В противном случае  $a_{j-1}=0$ ,  $q_{j-1}=q_j+0=0$ .

2 Определяется остаток  $R=A_i-C_{n-1}^{k-q_j}$  , если  $a_{j-1}=1$  или  $R=A_i$  при  $a_{j-1}=0$  .

3 Сравнивается остаток R с весом (j- 2)-го разряда  $C_{n-1}^{k-q_{j-1}}$  . Если  $R \ge C_{n-1}^{k-q_{j-1}}$  , то  $a_{j-2}=1$  ,  $q_{j-2}=q_{j-1}+1$  . В противном случае  $a_{j-2}=0$  ,  $q_{j-2}=q_{j-1}+0$  .

4 Определяется коэффициент  $a_{j-3}$ ,  $a_{j-4}$ , ... и т.д. по аналогии с пунктом 2, 3 до тех пор, пока кодовая комбинация не станет удовлетворять условиям биномиального числа.

5 Коэффициент  $a_l$ , где l=j - 1, j - 2, ..., 0, при котором выполняются условия биномиального числа, является коэффициентом  $a_0$ .

**Пример** Перевести число  $A_i = 2$  в биномиальную систему счисления с n = 6 , k = 4 .

Так как  $\ A_2=2 < C_5^4=5$  , то  $\ a_{j-1}=0$  ,  $\ q_{j-1}=q_j+0=0+0=0$  . Из того, что  $\ R=A_2=2 > C_{6-2}^{4-0}=1$  , следует  $\ a_{j-2}=1$  ,  $\ q_{j-2}=q_{j-1}+1=0+1=1$  .

Определяется остаток  $R_1=R-C_{6-2}^{4-0}=1$ . Вес (j-3)-го разряда равен  $C_{6-3}^{4-1}=1$ . Так как  $R=C_{6-3}^{4-1}$ , то  $a_{j-3}=1$ ,  $q_{j-3}=q_{j-2}+1=2$ . Определяется новый остаток  $R_2=R-C_{6-3}^{4-1}=0$ . Вес (j-4)-го разряда равен  $C_{6-4}^{4-2}=1$ , а  $a_{j-4}=0$  (  $R_2=0< C_{6-4}^{4-2}=1$ ). После появления коэффициента  $a_{j-4}=0$  число нулей в комбинации  $a_{j-1}$ ,  $a_{j-2}$ ,  $a_{j-3}$ ,  $a_{j-4}=0$ 110 достигло двух, что соответствует определению биномиального числа.

Наличие ограничений на число единиц k и число нулей l позволяет обнаруживать ошибки в биномиальных числах. Для этого необходимо дополнить кодовые комбинации их нулями до длины n-1. В табл. 3 для n=6, l=4, k=2 приведены биномиальные комбинации с одинаковым числом разрядов. Ошибка будет обнаруживаться в случае, когда число единиц в комбинации будет больше двух, например, комбинация 00111 является ошибочной. Ошибка будет также и в случае, если число нулей перед последней единицей больше или равно n-k.

Таблина 3

| Пор. | Равномерная<br>биномиальная<br>комбинация | Пор.<br>ном. | Равномерная<br>биномиальная<br>комбинация | Пор.<br>ном. | Равномерная<br>биномиальная<br>комбинация | Пор.<br>ном. | Равномерная<br>биномиальная<br>комбинация |

|------|-------------------------------------------|--------------|-------------------------------------------|--------------|-------------------------------------------|--------------|-------------------------------------------|

| 0    | 00000                                     | 4            | 00101                                     | 8            | 01010                                     | 12           | 10010                                     |

| 1    | 00010                                     | 5            | 00110                                     | 9            | 01100                                     | 13           | 10100                                     |

| 2    | 00011                                     | 6            | 01000                                     | 10           | 10000                                     | 14           | 11000                                     |

| 3    | 00100                                     | 7            | 01001                                     | 11           | 10001                                     |              |                                           |

Из табл. 3 видно, что имеется 17 запрещенных комбинаций, из них одна (00001) обнаруживается на основе второго условия, остальные - с помощью первого. Таким образом, данный код эффективен для ошибок, носящих асимметричный характер типа  $0 \to 1$ . В случае другого характера ошибок, вплоть до симметричного, степень асимметрии регулируется изменением k.

На основе предложенного алгоритма перебора биномиальных чисел был реализован помехоустойчивый счетчик с асимметричным характером исправляемых ошибок.

Таким образом, предложенные алгоритмы, использующие биномиальные числа, решают задачи перебора и генерирования кодов с постоянным весом и позволяют разрабатывать помехоустойчивые суммирующие и вычитающие счетчики.

#### Список литературы

- 1. *Березюк Н. Г.*, *Андрущенко А. Г.*, *Мощицкий С.С.* Кодирование информации. Х.: Вища шк. Изд-во при Харьк. ун-те, 1978. 252 с.

- 2. *Цымбал В. П.* Теория информации и кодирование. К.: Вища шк., Головное изд-во, 1977. 287 с.

- 3. *Борисенко А. А.* Система с биномиальным основанием и двоичным алфавитом, ВИНИТИ. М., 1982 , № 909 88. -6 с.

# 1.7 Биноминальные микропроцессорные устройства для перебора равновесных кодов

А.А. Борисенко, канд. техн. наук, А.Л. Верхоробин, В.Н. Кузнецов, канд. техн. наук

Автоматизированные системы управления и приборы автоматики, Харьков, № 96, 1990 г.

Равновесные коды (коды с постоянным числом единиц) вследствие простоты алгоритмов кодирования и декодирования и высокой помехообнаруживающей способности широко применяются на практике как для передачи данных по каналам связи, так и при хранении и передаче информации в цифровых системах обработки информации [1, 2].

Как правило, формирование равновесных кодов происходит на основе таблиц, что ограничивает их разрядность и соответственно мощность. Это не позволяет в полной мере использовать достоинства равновесных кодов и ограничивает область их применения.

Рассмотрим помехоустойчивый алгоритм перебора равновесных кодов повышенной мощности на основе биномиальных чисел и реализацию на его основе помехоустойчивого микропроцессорного устройства. С его помощью легко решается задача перевода двоичных кодов в равновесные, а также задача счета в помехоустойчивом коде, что имеет особое значение в системах телеавтоматики [2].

Алгоритм работы устройства основывается на правилах выполнения арифметических операций в биномиальной системе счисления [3].

**Определение**. k - биномиальным числом называется двоичная комбинация разрядности n, содержащая не более k единиц u l=n-k+1 нулей до младшей единицы или k единиц u l< n-k нулей до младшей единицы .

Например, для n=5, k=2 число 00001 не является биномиальным, так как перед младшей единицей, стоящей в нулевом разряде, находятся четыре нуля, а должно быть не более n-k=5-2=3. Число 00110 является биномиальным, так как содержит k=2 единицы и 2<3 нуля до младшей единицы, стоящей в первом разряде.

Работа рассматриваемого устройства происходит по следующим правилам:

- 1 В исходном состоянии все разряды устройства установлены в нуль.

- 2 Происходит занесение единицы в (k-i)-й разряд, где i число единиц в разрядной сетке устройства.

- 3 Подсчитывается число единиц в ней.

- 4 Если число единиц меньше k, то переход к пункту 2.

- 5 Если число единиц равно k и они не расположены в k старших разрядах, то младшие единичные разряды до первого нулевого устанавливаются в нуль, а первый нулевой в единицу.

- 6 Если число единиц равно k и они расположены в k старших разрядах, то цикл счета окончен.

- 7 Если число единиц больше k, то вырабатывается сигнал «ошибка» и происходит переход к пункту 1.

- 8 Производится подсчет числа нулей в разрядной сетке устройства до первой младшей единицы.

- 9 Если число нулей меньше или равно n-k+1, то переход к п. 2.

- 10 Если число нулей больше n-k+1, то вырабатывается сигнал «ошибка» и происходит возврат к пункту 1.

Количество перебираемых устройством биномиальных чисел определяется из выражения

$$N = C_{n+1}^{k} = \frac{(n+1)}{k!(n-k+1)!}.$$

В таблице 1 в качестве примера приведены биномиальные числа с  $n=5,\ k=2,\$ полученные в соответствии с приведенным выше алгоритмом.

Таблица 1

| Номер | 54321 | Номер | 54321 | Номер | 54321 | Номер | 54321 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 00000 | 4     | 00101 | 8     | 01010 | 12    | 10010 |

| 1     | 00010 | 5     | 00110 | 9     | 01100 | 13    | 10100 |

| 2     | 00011 | 6     | 01000 | 10    | 10000 | 14    | 11000 |

| 3     | 00100 | 7     | 01001 | 11    | 10001 | 15    |       |

Переход к равновесной комбинации от биномиальной осуществляется приписыванием к последней единиц, если она их содержит меньше k, или нулей, если она содержит k единиц. Единицы приписываются, начиная от (n-k+1)-го нуля, а нули - от последней k -й единицы при счете от старшего разряда до тех пор, пока соответственно число единиц не станет равным k или число нулей - равным n-k+1 [5]. Так, биномиальная комбинация 01000 с n=5 и k=4 после преобразования в равновесную будет иметь вид 010111.

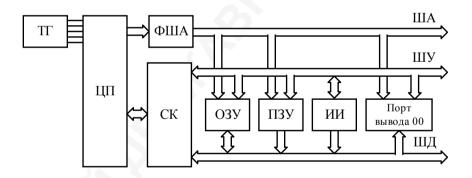

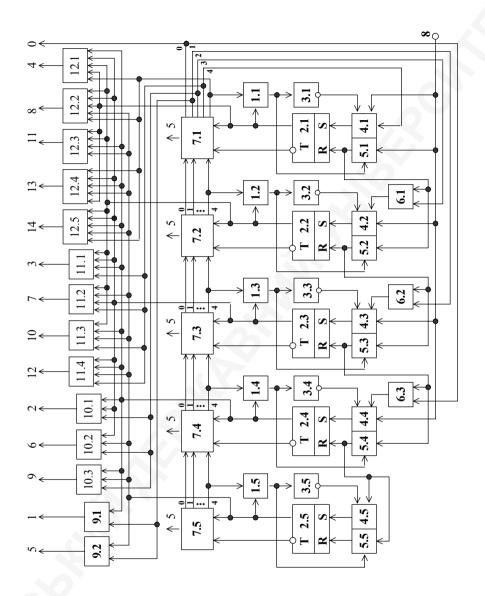

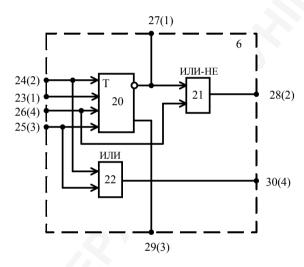

Тактовый генератор микропроцессорного устройства (МПУ) может быть собран на МС КР580ГФ24. Он вырабатывает последовательности синхроимпульсов, необходимые для нормальной работы устройства. Формирователь шины адреса (ФША) буферирует адресные лини МП и может быть реализован на двух МС КР580ВА86. Системный контроллер (СК) буферирует шину данных (ШД) и вырабатывает управляющие сигналы, необходимые для работы внешних по отношению к ЦП устройств.

В начальный момент времени ЦП находится в состоянии ожидания (или может выполнять какие-либо дополнительные функции, не относящиеся к биномиальному счетчику). Источник информации (ИИ) посылает запрос на прерывание и вырабатывает команду RST, которая вызывает подпрограмму биномиального счетчика, хранящуюся в ПЗУ. При каждом обращении к подпрограмме содержимое счетчика увеличивается на единицу и выводится в порт вывода 00, который в данном случае является потребителем информации. При обнаружении ошибки в работе счетчика микропроцессор выводит сообщение об ошибке также в порт вывода 00, после чего счетчик обнуляется и

продолжает работать в прежнем режиме.

ОЗУ используется для хранения предыдущего состояния счетчика и организации стека, который необходим при работе с подпрограммами. Таким образом, объем ОЗУ, необходимый непосредственно для биномиального счетчика, составляет всего несколько ячеек.

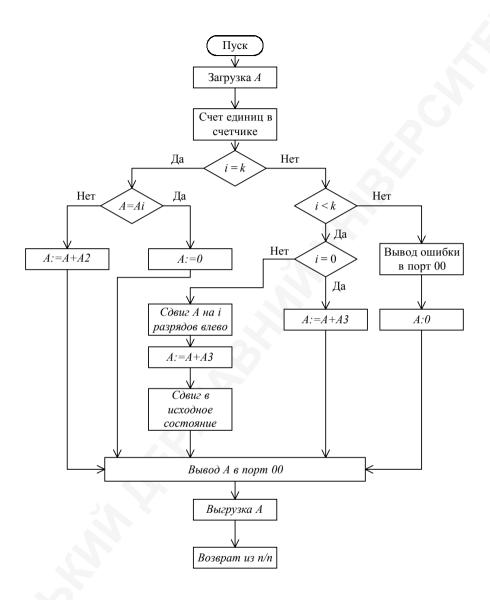

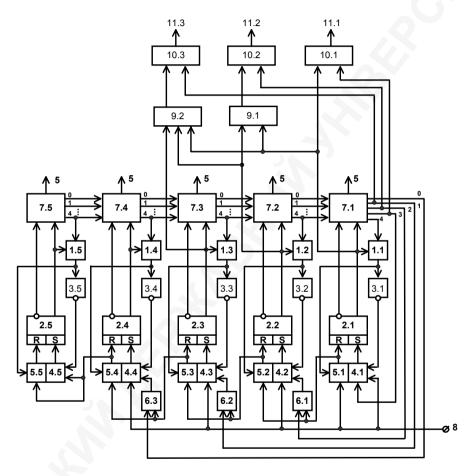

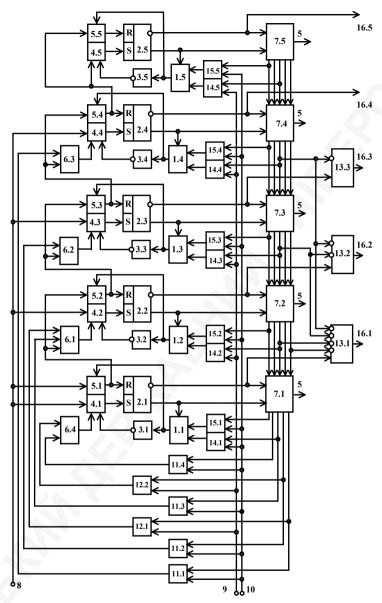

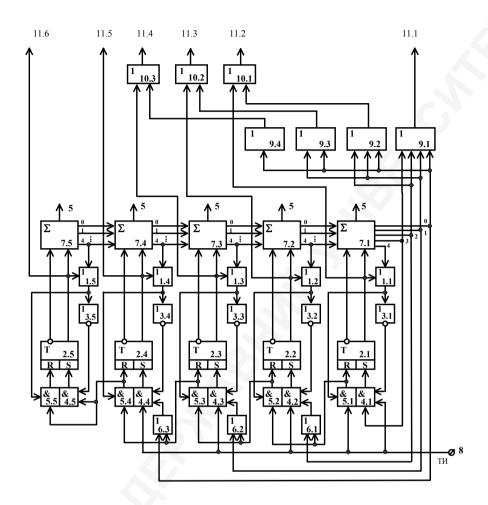

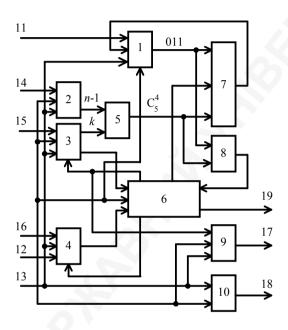

Блок-схема алгоритма работы подпрограммы биномиального счетчика представлена на рис. 1.

При обращении к подпрограмме в аккумулятор загружается число A (предыдущее состояние счетчика, которое хранится в счетчике ОЗУ). Для перехода к следующему состоянию нам необходимо знать, какое количество единиц уже содержится в счетчике, поэтому на следующем этапе подсчитывается число единиц (1). Дальше алгоритм разветвляется в зависимости от того, равно ли количество единиц контрольному числу (i=k?). В случае равенства проверяется, находятся ли все единицы в старших разрядах счетчика (A=A1?), и в зависимости от результата обнуляется счетчик (A:=0) или прибавляется единица в младший разряд счетчика (A:=A+A2).

Рисунок 1- Блок-схема алгоритма работы подпрограммы биномиального счетчика

Случай, когда i не равно k, в свою очередь, делится на два варианта: i > k и i < k. Если число единиц в счетчике больше контрольного числа (i > k), то это значит, что произошла ошибка. В этом случае выводится в порт 00 сообщение об ошибке, после чего обнуляется счетчик (A:=0).

Если число единиц в счетчике меньше контрольного числа

(i < k), то алгоритм также разветвляется в зависимости от того, равно нулю число единиц или нет (i = 0?). В случае равенства нулю нужно прибавить единицу в разряд счетчика с номером k (A: =A + A3), а в случае неравенства необходимо сначала сдвинуть содержимое счетчика на i разрядов влево, а после сложения вернуть его в исходное состояние.

Окончание программы для всех рассмотренных случаев одно и то же: выводится новое состояние счетчика в порт вывода 00, затем выгружается в ячейку ОЗУ для хранения до следующего обращения к подпрограмме и происходит возврат из подпрограммы.

Подпрограмма биномиального счетчика на языке Ассемблера представлена ниже. Очевидно, что на одном микропроцессоре можно организовать несколько биномиальных счетчиков с различными параметрами. При этом различные источники информации будут выдавать запросы на прерывания и формировать различные команды *RST*. В свою очередь, микропроцессор будет поочередно обрабатывать запросы и выдавать информацию в различные порты вывода.

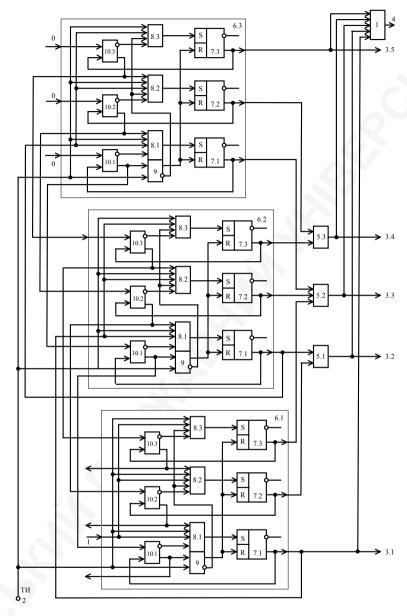

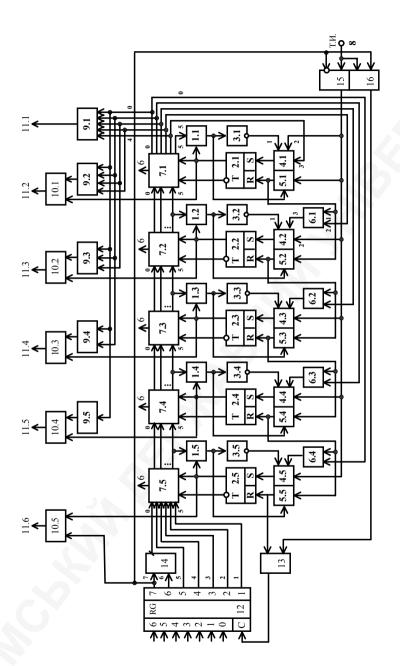

Если же микропроцессор будет использоваться для реализации одного единственного счетчика и никаких дополнительных функций выполнять не будет, то можно исключить из структурной схемы, изображенной на рис. 2, ОЗУ, а предыдущее состояние счетчика хранить в регистре микропроцессора. При этом будет единственный порт вывода, который можно будет не соединять с шиной адреса. В этом случае можно обойтись без формирователя шины адреса.

### Список литературы

- 1. Дж. Мартин. Системный анализ передачи данных. М., 1975.- Т.1.- С. 10 15.

- 2. Тутевич В. Н. Телемеханика. М., 1985. 200 с.

- 3. Борисенко А. А., Губарев С. И., Куно Г. В. Биномиальные системы счисления с двоичным алфавитом // АСУ и приборы автоматики. 1985. Вып. 76. С. 87 93.

- 4. *Борисенко А. А., Пузько Н. Д., Куно Г. В.* Биномиальные двоичные счетчики // Информ. листок. № 84 132. X., 1984.

- 5. Борисенко А. А., Губарев С. И., Куно Г. В. Алгоритмы построения кодов с постоянным весом на основе биномиальных чисел // АСУ и приборы автоматики. 1985. Вып. 74. С. 77 81.

Рисунок 2 - Структурная схема биномиального микропроцессорного устройства для перебора кодов

## ОПРЕДЕЛЕНИЯ

### АССЕМБЛЕР МП К580ИК80А

##

| BINOM -     | — ПОДПРОГРАММ                    | ла биномиального двоичного счетчи                                       |

|-------------|----------------------------------|-------------------------------------------------------------------------|

|             | ЗУЕМЫЕ РЕГИСТР<br>ЗУЕМЫЕ ПОДПРОІ | ГРАММЫ: HET                                                             |

| ADR E       | QU 0F100H                        | ОПРЕДЕЛЕНИЯ<br>;АДРЕС ЯЧЕЙКИ ХРАНЕНИЯ ПРЕДЫДУЩЕГО<br>СОСТОЯНИЯ СЧЕТЧИКА |

| N           | EQU 5                            | ;N—ЧИСЛО РАЗРЯДОВ СЧЕТЧИКА                                              |

| K<br>A1     | EQU 4<br>EQU 11110000B           | ;К—КОНТРОЛЬНОЕ ЧИСЛО<br>;ЧИСЛО СО ВСЕМИ ЕДИНИЦАМИ                       |

| A2          | EQU 00001000B                    | ;В К СТАРШИХ РАЗРЯДАХ<br>;ЕДИНИЦА МЛАДШЕГО РАЗРЯДА                      |

| A3          | EQU 01000000B                    | ;ЕДИНИЦА В РАЗРЯДЕ К                                                    |

| ;           | СЧЕТЧИК ИСПО                     | ОЛЬЗУЕТ N СТАРШИХ РАЗРЯДОВ ЩД МП<br>ПРОГРАММА                           |

| BINOM:      | LDA ADR                          | ;ЗАГРУЗКА ПРЕДЫДУЩЕГО СОСТОЯНИЯ<br>;БИНОМИАЛЬНОГО СЧЕТЧИКА              |

|             | MVI B, 0<br>MVI C, N             | ;СБРОС СЧЕТЧИКА ЕДИНИЦ: I = 0<br>;ЗАГРУЗКА КОЛИЧЕСТВА РАЗРЯДОВ БИН.     |

|             |                                  | СЧЕТЧИКА                                                                |

| ;           |                                  | ІНИЦ ПУТЕМ СДВИГА РАЗРЯДОВ<br>Т «С» РЕГИСТРА УСЛОВИЙ                    |

| ,<br>LAB10: | RLC                              | :СДВИГ                                                                  |

|             | JNC LAB20                        | ;БИТ «С» РАВЕН НУЛЮ?                                                    |

| LAB20:      | INR B<br>DCR C                   | ;НЕТ ТОГДА УВЕЛИЧИВАЕМ ЧИСЛО ЕДИНИЦ<br>;ПЕРЕХОДИМ К СЛЕДУЮЩЕМУ РАЗРЯДУ. |

|             | JNZ LAB10<br>REPT 8—N            | ;СЧЕТ ОКОНЧЕН? НЕТ - ТОГДА ПОВТОРИМ ;ВОЗВРАТ БИН. СЧЕТЧИКА В ИСХОДНОЕ   |

|             | RLC                              | ;СОСТОЯНИЕ;                                                             |

|             | ENDM                             |                                                                         |

| :           | СРАВНЕНИЕ КОЛ-                   | ;<br>ВА ЕДИНИЦ «1» С КОНТРОЛЬНЫМ ЧИСЛОМ « <i>k</i> »                    |